### **Factsheet**

# IEEE 1394a eVC - SI170FWAeV20

## eVC IEEE 1394a-2000 Link Layer **Controller** VIP

Silicon Interfaces' IEEE 1394a-2000 Link Layer Controller eVC is a fully documented, off the shelf component for Cadence Specman Elite<sup>TM</sup> functional verification environment.

The IEEE 1394 a-2000 link layer controller (from now on referred to only as 1394a) provides connectionless acknowledged data transfer services between a source node and destination node where node is an addressable device attached to the serial bus with at least a minimum set of control registers.

eVCs are configurable, reusable verification components written in the e language and designed to simplify and speed up the verification tasks. These comprise a complete verification environment including stimulus generation, checking, monitoring and functional coverage. eVCs provide major increase in the productivity and higher quality products.

The IEEE 1394a Function Controller eVC verifies designs that include IEEE 1394a Function Controller. This eVC accurately verifies and ensures that the particular function controller is satisfying the IEEE 1394a protocol, as well as thoroughly exercises the link controller.

The eVC supports IEEE 1394a PHY specification at the Physical side and Transaction Layer specification at the Host side. Data transmission can be configured to be at 100, 200 or 400 Mbps and can also be configured to be asynchronous or isochronous transaction.

# Silicon Cores

Core to the Intelligent System<sup>T</sup>

#### **Product Highlights**

- ☑ Fully compliant with the IEEE 1394a specifications

- ☑ Totally configurable, as per user requirements

- ☑ Can operate at 100 Mbps, 200Mbps and 400 Mbps

- ☑ Supports IEEE 1394a PHY interface at Physical side and Application, Transaction layer and Serial Bus Manager features at the Host side

- ☑ Protocol Compliance checking

- ✓ Can be configured to be in root and non-root mode to check generation and reception of cycle start packet

- **☑** Random generation of Asynchronous and Isochronous data packets

- ☑ Covers all types of transaction

- ✓ Compares driven data packets with received data packets

- ✓ Computing CRC of data packets

Provides CRC error notification

- ☑ Configuration and reading of CSR's

- $\mathbf{Q}$ The monitors the various transactions and their sequences.

- ☑ Perl script makes configuration easier

- ☑ HDL independent.

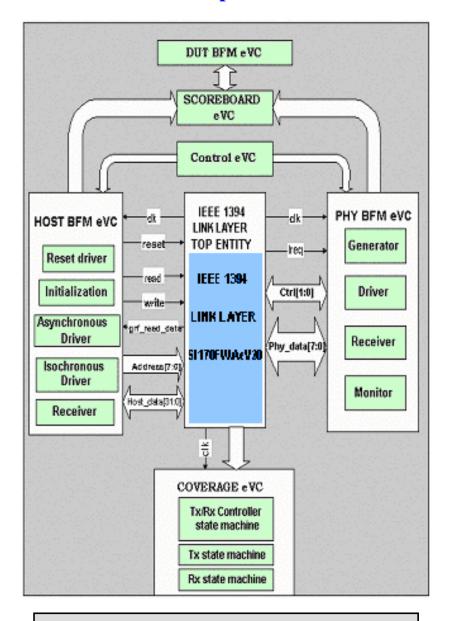

#### **IEEE 1394a Block Representative Schematic**

Contact:

Email: info@siliconinterfaces.com

Phone: (+91-22) 2491 3024; Fax: (+91-22) 2498 1379 In USA: (+1-408) 866 2458; Fax: (+1-408) 866 6586 In UK: (+44-20) 8543 4436; Fax: (+44-20) 8544 1311

Notice: Information in this document is indicative. Product specifications are subject to change without notice. Silicon Interfaces shall not be responsible for direct, indirect or consequential damages that may accrue through typographical errors or otherwise. No license, expressed or implied to any intellectual property rights is granted by this document. Product names mentioned herein may be trademarks and/or registered trademarks of their respective owners. Rights are hereby acknowledged.

#### Verification Methodology:

An IEEE 1394a Link Layer Controller eVC initiates the IEEE 1394a PHY layer and Transaction and Application layer compliant transactions. These transactions are applied to the Device under Test (DUT) and as well as to the eVC Device.

The PHY BFM is a model of the PHY layer of the protocol, which on one side interfaces with the link layer (SI70FW11) and on the other side with the serial bus. The HOST BFM emulates the Transaction layer, Application layer and the Serial Bus Manager features. Both the HOST and the PHY BFM's generate, transmit and receive Protocol data units.

The data checker, which is implemented in the form of scoreboard, compares the data collected at the HOST or the PHY receiver with the data driven from the PHY or HOST transmitter respectively, thus verifying adherence to the IEEE 1394a protocol.

At all the times the eVC monitors signals at the HOST and PHY Bus function model interface. Coverage block covers all the states defined in the DUT main state machines and reports whenever an illegal transition occurs.

# Silicon Interfaces® a software and vlsi design center

a software and visi design center

Silicon Interfaces is the world's answer to integrated solutions for Design Services needs for SOC, ASIC & FPGA for Wireless, Cable & Optical Networking, Fiber Channel & Interconnect, Data Communications and Storage. Silicon Interfaces is operating since 1990 primarily in USA, Europe and Pacific Rim.